玻璃通孔三维互连镀铜填充技术发展现状

收稿日期: 2021-11-08

修回日期: 2022-01-21

网络出版日期: 2022-03-04

Development Status of Copper Electroplating Filling Technology in Through Glass Via for 3D Interconnections

Received date: 2021-11-08

Revised date: 2022-01-21

Online published: 2022-03-04

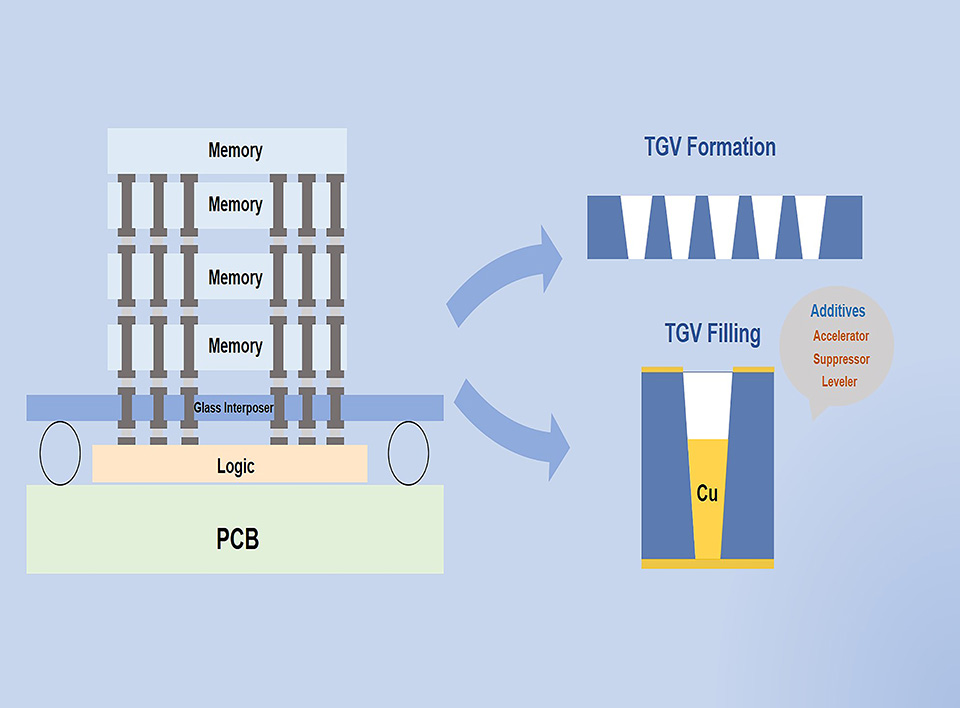

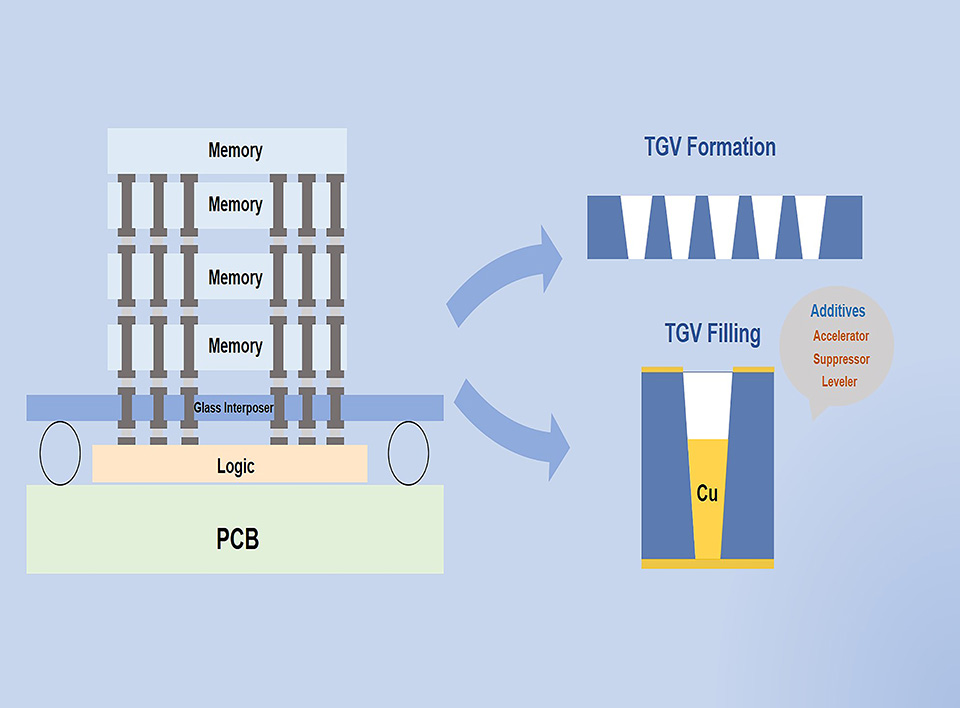

随着摩尔定律的发展迟缓,微电子器件的高密度化、微型化对先进封装技术提出了更高的要求。中介层技术作为2.5D/3D封装中的关键技术,受到了广泛研究。按照中介层材料不同,主要分为有机中介层、硅中介层以及玻璃中介层。与硅通孔(through silicon via, TSV)互连相比,玻璃通孔(through glass via,TGV)中介层(interposer)因其具有优良的高频电学特性、 工艺简单、 成本低以及可调的热膨胀系数(coefficient of thermal expansion,CTE)等优点,在2.5D/3D先进封装领域受到广泛关注。然而玻璃的导热系数(约1 W·m-1·K-1)与硅(约150 W·m-1·K-1)相比要低很多,因此玻璃中介层存在着严重的散热问题。为得到高质量的TGV中介层,不仅需要高效低成本的通孔制备工艺,还需要无缺陷的填充工艺,目前玻璃中介层面临的挑战也主要集中在这两方面。本文首先介绍了TGV的制备工艺,如超声波钻孔(ultra-sonic drilling, USD)、超声波高速钻孔(ultra-sonic high speed drilling,USHD)、湿法刻蚀、深反应离子刻蚀(deep reactive ion etching, DRIE)、光敏玻璃、激光刻蚀、激光诱导深度刻蚀(laser induced deep etching, LIDE)等。接着围绕TGV的无缺陷填充进行总结,概述了TGV的几种填充机理以及一些填充工艺,如bottom-up填充、蝶形填充以及conformal填充。然后对TGV电镀添加剂的研究进展进行了介绍,包括典型添加剂的作用机理以及一些新型添加剂的研究现状,最后并对TGV实际应用情况进行了简要综述。

纪执敬 , 凌惠琴 , 吴培林 , 余瑞益 , 于大全 , 李明 . 玻璃通孔三维互连镀铜填充技术发展现状[J]. 电化学, 2022 , 28(6) : 2104461 . DOI: 10.13208/j.electrochem.210446

With the slow development of Moore's Law, the high density and miniaturization of microelectronic devices put forward higher requirements for advanced packaging technology. As a key technology in 2.5D/3D packaging, interposer technology has been extensively studied. According to different interposer materials, it is mainly divided into organic interposer, silicon interposer and glass interposer. Compared with the through silicon via (TSV) interconnection, the through glass via (TGV) interposer has received extensive attention in the 2.5D/3D advanced packaging field for its advantages of excellent high-frequency electrical characteristics, simple process, low cost, and adjustable coefficient of thermal expansion (CTE). However, the thermal conductivity of glass (about 1 W·m-1·K-1) is much lower than that of silicon (about 150 W·m-1·K-1), thus, the glass interposer has serious heat dissipation problems. In order to obtain a high-quality TGV interposer, not only an efficient and low-cost via preparation process, but also a defect-free filling process is required. The challenges faced by glass interposer is mainly concentrated in these two aspects. This review firstly introduces the preparation process of TGV, such as ultra-sonic drilling (USD), ultra-sonic high speed drilling (USHD), wet etching, deep reactive ion etching (DRIE), photosensitive glass, laser etching, laser induced deep etching (LIDE), etc. Then it summarizes the defect-free filling of TGV, and outlines several filling mechanisms and some current filling processes of TGV, such as bottom-up filling mechanisms, butterfly filling mechanisms and conformal filling mechanisms. Among the filling mechanisms of the above three filling methods, the filling method of bottom-up is the most studied one, and many scholars have given relevant explanations. Currently, the main ones that are commonly used are the diffusion-consumption mechanism, curvature enhanced adsorbate coverage mechanism (CEAC), convection dependent adsorption mechanism (CDA), and S-shaped negative differential resistance theory. In the process of TGV filling, the type and concentration of base bath, additives and electroplating process will affect the filling status of TGV. At present, the constant current plating mode is most commonly used in the process of TGV filling. Then the research progress of TGV electroplating additives is introduced, including the action mechanism of typical additives and the current research status of some new additives. Through glass via technology can be filled with the synergistic action of accelerators, suppressors and levelers. Finally, the practical application of TGV is briefly reviewed, for example, glass interposer is used in 3D integrated passive device (IPD), embedded glass fan-out technology (eGFO), integrated antenna packaging, micro-electro-mechanical system (MEMS), multi-chip module packaging, as well as the applications in the field of optical integration technology.

Key words: interposer; through glass via; filling mechanisms; filling process; additives

/

| 〈 |

|

〉 |